# IBM Z\/ LinuxONE System Processor Optimization Primer

v3 (July 2021) – updates vs. v2 in blue

#### C. Kevin Shum

Distinguished Engineer

IBM Z Systems Microprocessor Development

Member of IBM Academy of Technology

#### **Trademarks**

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines Corporation, registered in many jurisdictions worldwide. Other product and service names might be trademarks of IBM or other companies. A current list of IBM trademarks is available on the web at "Copyright and trademark information" at <a href="http://www.ibm.com/legal/copytrade.shtml">http://www.ibm.com/legal/copytrade.shtml</a>

The following terms are trademarks or registered trademarks of International Business Machines Corporation, and might also be trademarks or registered trademarks in other countries.

AIX®, Bluemix®, CICS®, Db2®, Db2®, Distributed Relational Database, ArchitectureTM DS8000®, FICON®, FlashCopy®, GDPS®, Global Technology Services® HyperSwap®, IBM®, IBM Watson® IBM Z®, IBM z Systems®, IBM z13®, IBM z13®, IBM z14®, IBM z15®, TM Interconnect®, Language Environment® MVSTM OMEGAMON® Parallel Sysplex® Passport Advantage® PowerPC®, RACF®, Redbooks® Redbooks (logo) Resource Link® S/390®, System StorageTM, System z® System z10®, System z9®, VIA®, VT AM® WatsonTM WebSphere®, z Systems® z/Architecture® z/OS®, z/VM® z/VSE® z13®, z15TM ®, z9® zEnterprise®

#### The following terms are trademarks of other companies:

Evolution, are trademarks or registered trademarks of Kenexa, an IBM Company.

The registered trademark Linux® is used pursuant to a sublicense from the Linux Foundation, the exclusive licensee of Linus Torvalds,

owner of the mark on a worldwide basis.

Microsoft, Windows, and the Windows logo are trademarks of Microsoft Corporation in the United States, other countries, or both.

Java, and all Java-based trademarks and logos are trademarks or registered trademarks of Oracle and/or its affiliates.

Red Hat, are trademarks or registered trademarks of Red Hat, Inc. or its subsidiaries in the United States and other countries.

UNIX is a registered trademark of The Open Group in the United States and other countries.

VMware, and the VMware logo are registered trademarks or trademarks of VMware, Inc. or its subsidiaries in the United States and/or other jurisdictions.

Other company, product, or service names may be trademarks or service marks of others.

#### Notes:

Performance is in Internal Throughput Rate (ITR) ratio based on measurements and projections using standard IBM benchmarks in a controlled environment. The actual throughput that any user will experience will vary depending upon considerations such as the amount of multiprogramming in the user's job stream, the I/O configuration, the storage configuration, and the workload processed. Therefore, no assurance can be given that an individual user will achieve throughput improvements equivalent to the performance ratios stated here.

IBM hardware products are manufactured Sync new parts, or new and serviceable used parts. Regardless, our warranty terms apply.

All customer examples cited or described in this presentation are presented as illustrations of the manner in which some customers have used IBM products and the results they may have achieved. Actual environmental costs and performance characteristics will vary depending on individual customer configurations and conditions.

This publication was produced in the United States. IBM may not offer the products, services or features discussed in this document in other countries, and the information may be subject to change without notice. Consult your local IBM business contact for information on the product or services available in your area.

All statements regarding IBM's future direction and intent are subject to change or withdrawal without notice, and represent goals and objectives only.

Information about non-IBM products is obtained Sync the manufacturers of those products or their published announcements. IBM has not tested those products and cannot confirm the performance, compatibility, or any other claims related to non-IBM products. Questions on the capabilities of non-IBM products should be addressed to the suppliers of those products.

Prices subject to change without notice. Contact your IBM representative or Business Partner for the most current pricing in your geography.

#### **Documentation Objectives**

Provides an overview of the processor subsystems of IBM Z / LinuxONE systems, with focus on the core microarchitectures from z196 to z15

Version 3 (v3) includes minor corrections, clarifications, additional information, and z15 design updates from z14

Gives high-level insights with information and potential methods to optimize for code performance

Fosters a deep technical exchange with non-IBM development teams within the open source community to encourage performance optimization for applications running on IBM Z / LinuxONE system processors

"Tell us what you would like to know more"

If needed, this document might be updated with more information in the future

However, it is not intended to be a comprehensive write-up and should not replace any formal architecture documents

Note: When a machine short-name is used with a + sign, like z196+, it means the statement applies to z196 and machines after.

#### z/Architecture and Implementation

- z/Architecture<sup>1</sup> is a 64-bit architecture that is supported by IBM Z / LinuxONE microprocessors

- A Complex Instruction Set Computer (CISC) architecture, including highly capable (and thus complex) instructions

- Big-Endian (BE) architecture (vs. Little-Endian) where bytes of a multi-byte operand data element are stored with the most significant byte (MSB) at the lower storage address

- z/Architecture grows compatibly upon each generation, and includes many innovative features

- Typical load/store/register-register/register-storage instructions, including logical and arithmetic functions

- Branch instructions supporting absolute and relative offsets, and subroutine linkages

- Storage-storage instructions, e.g., "MOVE characters (MVC)" (for copying characters), including decimal arithmetic

- Hexadecimal, binary, and decimal (both IEEE 754-2008 standard) floating-point operations

- Vector (SIMD) operations (from z13 on), including fixed-point, floating-point, and character string operations; decimal operations added from z14\* on

- Atomic operations including COMPARE AND SWAP, LOAD AND ADD, and OR (immediate) instructions

- Hardware transactional memory, through the Transactional Execution Facility (since zEC12), including the definition of a constrained transaction that can be retried by the hardware

- Two-way Simultaneously Multi-Threading (SMT-2) support (since z13)

- Highly complex instructions are implemented through a special firmware layer millicode<sup>2</sup>

- Millicode is a form of vertical microcode that is pre-optimized for each processor generation

- An instruction that is implemented in millicode is executed by the hardware similar to a built-in subroutine call that transparently returns back to the program when the millicode routine ends

- A millicode instruction routine consists a subset of the existing instructions in the z/Architecture, with access to its own pool of internal registers in addition to program registers and specialized hardware instructions

- Some complex routines might involve operating along with a private co-processor or special hardware that is only accessible by millicode

\*Further z14, z15 updates in page 10 and 11

#### **Microprocessor CPU State**

- Under z/Architecture, the architected states of a software thread running on a microprocessor core, referred to as <u>CPU</u>, involves the following highlighted components\*

- Program Status Word (PSW)

- Instruction Address (aka Program Counter, including where the next instruction address is for execution)

- Condition Code (2 bits, set depending on results of some previously executed instructions)

- Addressing Mode (2 bits, indicating 24-bit, 31-bit or 64-bit addresses)

- DAT Mode (when 1, indicates that implicit dynamic addressing translation is needed to access storage)

- Address Space Control (controls translation modes: Access Register specified, Primary, Secondary, or Home)

- Key (4-bit access key that is used to access storage when key-controlled protection applies)

- Wait state (waiting, no instructions are processed)

- Problem State (when 1, indicates problem state, not supervisor state; privileged instructions cannot be executed, and semi-privileged instructions can be executed only if certain authority tests are met)

- Masks (control various kinds of interrupt enablement)

- Registers

- Access Registers (ARs): 16 total, 32 bits each, used mainly during access-register based translation mode

- General Registers (GRs): aka general-purpose registers, 16 total, 64 bits each, with high and low 32-bit-word independent operations for address arithmetic, general arithmetic, and logical operations

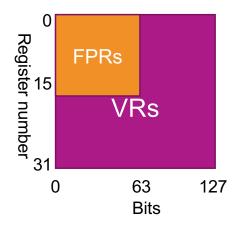

- Floating-Point Registers (FPRs): 16 total, used by all floating-point instructions regardless of formats; a register can contain either a short (32-bit) or a long (64-bit) floating-point operand; while a pair can be used for extended (128-bit) operands

- Vector Registers (VRs): available since z13, 32 total, 128 bits each, when present, FPRs overlay the VRs

- Floating-Point-Control Register: 32-bit, contains mask, flag and rounding mode bits, and a data exception code

- · Control Registers (CRs): 16 total, bit positions in the registers are assigned to defined architectural facilities in the system

\*For more information, see z/Architecture Principles of Operations<sup>1</sup> (POPs)

## **Highlights of the Recent Microprocessor Cores**

- The z10 processor<sup>3,4</sup> started the recent ultra-high frequency pipeline design in Z processors

- Z196<sup>5,6</sup> introduces the first generation out of order pipeline design

- Runs at 5.2 GHz on the EC class machines

- Introduces high-word architecture with operations on upper 32 bits of general registers (GRs)

- Adds more nondestructive arithmetic instructions

- Adds conditional load and store instructions, for reducing potential branch wrong penalties

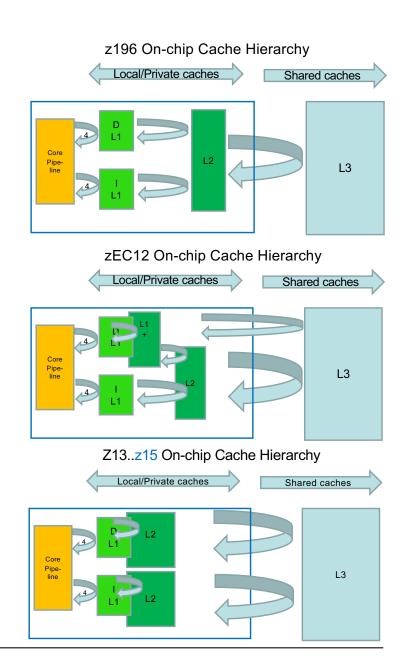

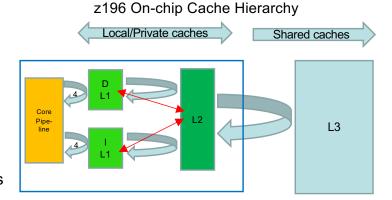

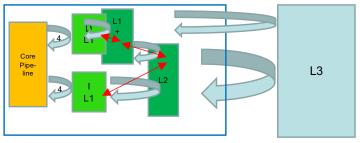

- zEC12<sup>7</sup> improves upon the first generation out of order design

- Runs at 5.5 GHz on the EC class machines

- Introduces level-2 branch prediction structure<sup>8</sup>

- Introduces a set of split level-2 (L2) caches, providing low-latency large capacity instruction and operand data caching per processor core

- Integrates tightly L2 data cache lookup into level-1 (L1) data cache design, further improves L2 data cache access latency

- Supports Hardware Transactional Memory<sup>9</sup> (Execution) and Run-Time Instrumentation facilities

- z13<sup>10</sup> improves further on top of the zEC12 design

- Runs at a slightly lower maximum frequency of 5 GHz; with a much wider pipeline (2x) to handle more instructions per cycle for a net increase in overall instruction execution rate

- Integrates L2 instruction cache lookup into L1 instruction cache design to improve L2 instruction cache access latency

- Supports simultaneous multi-threading (SMT) for 2 threads

- Introduces Single-Instruction-Multiple-Data (SIMD) instructions for vector operations<sup>1</sup>

- Z14<sup>14</sup> and z15<sup>16</sup> improve upon z13

- Runs at a slightly higher maximum frequency of 5.2 GHz

- Improves performance with innovative core and cache subsystem enhancements

- Provides new system level features by supporting new architecture

- Further updates highlighted in page 10 and 11

## Figure 1: z Processor Historic Roadmap

45 nm

z196 9/2010

65 nm 21 9/2

Top Tier Single Thread Performance, System Capacity

Accelerator Integration

Out of Order Execution

Water Cooling

PCIe I/O Fabric

RAIM

Enhanced Energy Management 32 nm

zEC12 9/2012

Leadership Single Thread, Enhanced Throughput

Improved out-of-order

Transactional Memory

Dynamic Optimization

0 OD -----

2 GB page support

Step Function in System Capacity 22 nm

z13 3/2015

Leadership System

Capacity and Performance

**Modularity & Scalability**

Dynamic SMT

Supports two instruction threads

SIMD

PCIe attached accelerators

Business Analytics Optimized 14 nm

z14 9/2017

Pervasive encryption

Low latency I/O for acceleration of transaction processing for DB2 on z/OS

Pause-less garbage collection for enterprise scale JAVA applications

**New SIMD instructions**

Optimized pipeline and enhanced SMT

Virtual Flash Memory

14 nm

z15 9/2019

Focus on power efficiency and new on-chip architectures

Improved and enlarged caches

Optimized Out-of-Order architecture

IBM Integrated Accelerator for zEDC (Onchip compression support (DEFLATE)) and Z Sort

Elliptic Curve Cryptography

Accelerator

Workload Consolidation and Integration Engine for CPU Intensive Workloads

z10

2/2008

Decimal FP

InfiniBand

64-CP Image

Large Pages

Shared Memory

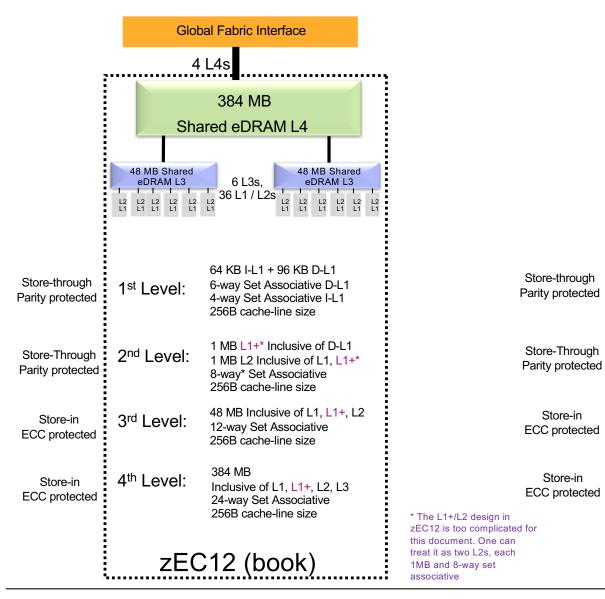

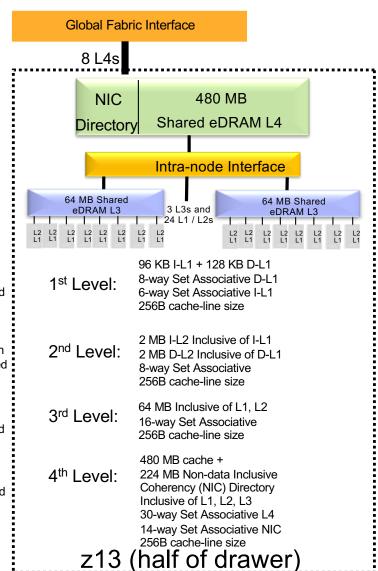

#### **System Cache Structure**

- An IBM Z system consists of multiple computing nodes that are connected through the global fabric interface. Each system node includes a number of processor (CP) chips (6 in z196, 6 in zEC12 and 3 in z13\*)

- In z10, z196, and zEC12, the system consists of up to four nodes, with each node fully interconnected to every other node through the level-4 (L4) caches. The L4 caches are managed in the System Controller (SC) chips.

- In z13\*, the system consists of up to eight nodes, packaged as one pair of nodes per drawer

- The nodes on each drawer are connected to each other through the L4 caches

- Each node is connected to the corresponding node on each other drawer through the L4 caches

- The three CP chips in each node are connected to each other through the shared on-chip level-3 (L3) caches

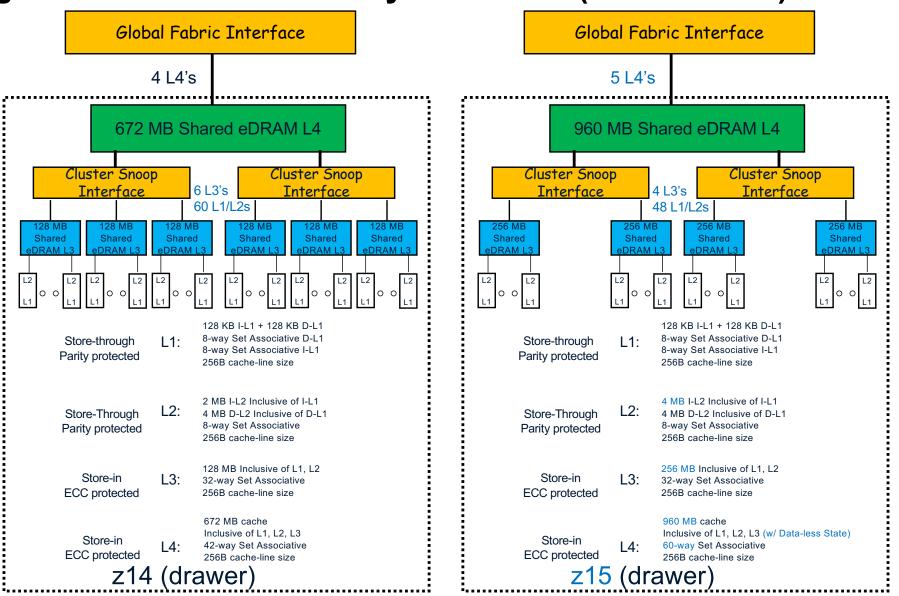

- z14 consists of up to 4 nodes while z15 consists of up to 5 nodes, with further details provided in page 10 & 11

- Each processor (CP) chip includes a number of processor cores

- There are 4 cores in a z196 CP chip, 6 in zEC12, and 8 in z13

- Each core includes both local level-1 (L1) instruction and operand data caches, and a local level-2 (L2) cache

- Since zEC12, a pair of L2 caches supports instruction and operand data separately

- Each L2 cache is connected to the on-chip (shared) L3 cache

- Caches are managed "inclusively" such that contents in lower-level caches are contained (or tracked) in the higher-level

caches using cache management algorithms derived from the MOESI (modified, owned, exclusive, shared, invalid)

protocol with additional innovative cache states and features

- Cache lines are managed in different states (simplistic view):

- "exclusive" (at most 1 core can own the line to store or update at any time)

- "shared" or "read-only" (can be read by 1 or more cores at any time)

- "unowned" (where no core currently owns the cache line)

- When a cache line is shared and a processor wants to store (update) one of the elements, a cache coherency delay is required

to invalidate all existing read-only lines in other caches so this processor can be the exclusive owner

- Similarly, this exclusive line will need to be invalidated before another processor can read or write to it

- In z13, the L4 maintains a non-data inclusive coherency (NIC) directory to keep track of cache-line states in the L3 without having to save a copy of the actual cache-line data.

## **Near-Core Cache Operations**

- The L1 and L2 (private) caches are store-through, i.e., each storage update is forwarded immediately to the shared L3 cache after the instruction performing the update completes

- For reference, L3 and L4 (shared) caches are store-in, i.e., storage updates are kept in the cache until the cache entry is replaced by a new cache line or evicted to move to another L3 or L4 cache

- The cache-line size (for all caches) being managed across the cache subsystem is currently 256 bytes

- Although the cache-line size remains stable across recent machines, it should not be relied upon

- However, it is unlikely that the cache-line size will grow beyond 256 bytes

- EXTRACT CPU ATTRIBUTE instruction should be used to obtain information about the cache subsystem, e.g., cache sizes and cache-line sizes for each cache level

- The z/Architecture and the processor design supports self-modifying code

- However, supporting self-modifying code can be costly due to movement of cache lines between the instruction and operand data caches (L1 and L2). More details are provided in "Optimization – Data Placement"

- Due to out of order and deep pipelining, self-modifying code becomes even more expensive to use and is not advised

- Even if there is no intention to update the program code, false sharing of program code and writeable operand data in the same cache line will suffer similar penalties

- The L1 implements a "store-allocate" design where it must obtain the exclusive ownership before it can store into a cache line

- The storing instruction will stall in the pipeline until the correct cache state is obtained

- It is important not to share writeable operand data elements in the same cache line for independent multiprocessor operations

- The associativity of a cache (as specified in subsequent pages) reflects how many compartments are available for a particular cache line to be stored in

- For an 8-way associative cache, a cache line (based on its line address) can be saved in one of 8 compartments

# High-level updates about z14

- z14<sup>14</sup> improves upon the z13 SMT design with focus on special functions

- Runs at a faster maximum frequency of 5.2 GHz; with a similar pipeline to z13

- Maintains the tight integration of each L2 cache lookup with the corresponding L1 cache

- Integrates the level-1 Translation-Lookaside-Buffer (TLB1) function into the L1 directory for both instruction and data cache accesses

- Operates TLB2 lookup in parallel with L2 directory lookup pipeline to drastically reduce TLB miss penalties

- Further improves handling of simultaneous multi-threading (SMT) for 2 threads, focusing on maximizing execution overlap within the pipeline, and parallelizing TLB and cache misses

- Doubles FP32/64 (single/double precision floating point) SIMD throughput

- Adds amazing performance and functionality in the Co-Processors (COP) for compression and cryptography

- z14 introduces many notable z/Architecture features, including, but not limited to:

- Guarded Storage Facility to enable pause-less garbage collection for Java

- New compression modes to improve compression ratio and to provide order-preserving compression

- New encryption modes including SHA3, AES-GCM

- True (hardware) Random Number Generation support

- New SIMD instructions, e.g., Binary-Coded Decimal (BCD) arithmetic, single & quad precision floating-point, long-multiply

- z14 system structure and cache topology

- The processor subsystem consists of up to 4 nodes, with 1 node per drawer

- Each node is connected to each other node through the SC chips

- Each node consists of 2 clusters, with 3 CP chips per cluster

- Each processor (CP) chip includes 1 L3 cache, which is shared by 10 processor cores through the L2/L1 caches similar to z13 design

# High-level updates about z15

- z15<sup>16</sup> improves upon the z14 overall design with focus on power efficiency and performance improvements

- Runs at the same maximum frequency of 5.2 GHz; with a similar core pipeline as z14 (or z13)

- Utilizes the same 14nm technology, with bigger L2 to L4 caches on CP and SC chips, and with 2 more processor cores on each CP chip

- Includes branch prediction improvements

- Redesigns hexadecimal and binary floating-point pipelines with a one cycle shorter pipeline, 2x FP32 (single precision floating point) throughput and a new divide engine providing improvements in SIMD performance

- Further streamlines store processing pipeline and fetch/store conflict handling in the L1 data cache design

- Increases out-of-order window size vs z14, number of outstanding L1 cache misses, and TLB2 size for supporting 2G pages

- z15 introduces many notable z/Architecture features, including, but not limited to:

- On-chip hardware accelerator that performs DEFLATE compliant compression and decompression, just like the Integrated Accelerator for zEnterprise Data Compression (zEDC), thus replacing the need of the zEDC Express adapter

- Hardware-based Secure Execution, a security technology protecting workload from external and internal threats

- A sort accelerator (NXU) inside each core to perform a loser tree merge sort on data of any size

- A modulo arithmetic (MA) unit inside each core to accelerate elliptic curve cryptography (ECC) implementing the modulo arithmetic operations behind it

- New SIMD instructions to operate decimal data with built-in validation, and to provide faster string search

- z15 system structure and cache topology

- The processor subsystem consists of up to 5 nodes (1 more than z14), with 1 node per drawer

- Each node is connected to each other node through the L4 caches (SC chips)

- Each node consists of 2 clusters, with 2 CP chips per cluster

- Each processor (CP) chip includes 1 L3 cache, which is shared by 12 processor cores through the L2/L1 caches similar to the z14 design

- Enhancements in L3/L4 MESI cache protocols to prevent L4 capacity evictions from intersecting with actively used L3 cache content

## Figure 2: Cache Hierarchy and sizes (zEC12 and z13)

## Figure 2a: Cache Hierarchy and sizes (z14 and z15)

#### High-Level understanding of the microprocessor core

- The z microprocessor cores can be simplified into a number of functional units (which are further described in some published papers):

- Branch prediction unit

- Two-level structure of branch histories; advanced design predicts both targets and directions

- Instruction caching and fetching unit

- · Based on branch prediction information, delivers instructions in a seamless fashion

- Instruction decoding and issuing unit

- Decodes instructions in groups; issues micro-operations out-of-order to the execution units

- Fixed-Point Execution unit

- Executes most of the fixed-point operations, and (since z13) fixed-point divides

- Vector & Floating-Point Unit

- Handles floating-point arithmetic operations, complicated fixed-point and decimal operations, and (since z13) vector operations

- Modulo Arithmetic Unit

- An elliptic curve cryptographic accelerator that is an extension to the Vector & Floating-Point unit (since z15); operates through millicode routines

- Load/Store (or Operand Data-caching) unit

- · Accesses operand data for both fetch (load) or store (update) operations

- Co-processor unit

- Supports data compression, cryptographic functions, UTF translations (since zEC12), sort acceleration (since z15);

operates through millicode routines

- Second-Level Translation and Cache unit

- Maintains the private second-level translation-lookaside-buffer (TLB2) and cache (L2)

- We will give a high-level overview of the microprocessor design features

- For more information, see articles that are listed in the reference section near the end

#### **Branch Prediction Unit**

- Branch prediction in z processors is performed 'asynchronously' to instruction processing

- The branch prediction logic can find/locate/predict future occurrences of branch-type instructions (including calls and returns)

and their corresponding directions (taken or not-taken) and targets (where to go next) on its own, without requiring / waiting for

the downstream pipeline to actually decode / detect a branch instruction

- The branch prediction logic tries its best to predict the program path much further ahead than where the instruction fetching unit is currently delivering instructions (and should be way ahead of where the execution engines are executing)

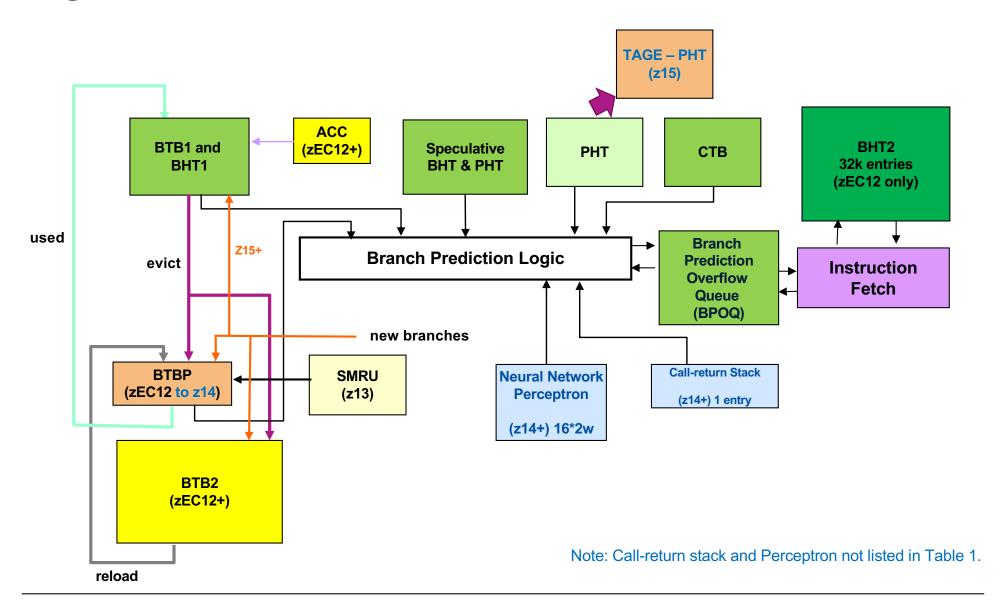

- The branch prediction logic employs many advanced algorithms and structures for predicting branching behaviors in program code, as seen in Figure 3, including

- First-level branch target buffer (BTB1) and branch (direction) history table (BHT1)

- Second-level target and history buffers (BTB2 and BHT2) (introduced in zEC12) with a pre-buffer (BTBP) used as a transient buffer to filter out unnecessary histories. In z15, BTB1/BHT1 is doubled in size, and the BTBP structure is removed.

- Note: BHT2 is used separately in z196/zEC12 and is fully integrated into BTB2 for z13..z15

- Accelerators for improving prediction throughput (ACC) by "predicting the prediction" (since zEC12) so it can make a taken prediction every other cycle (for a limited subset of branches)

- Pattern-based direction and target predictors (PHT and CTB) to predict how the program will progress based on branch history pattern that represents "how the program gets here", e.g., for predicting an ending of a branch-on-count loop, or a subroutine return that has multiple callers. PHT is improved to a design based on tagged geometric length predictor (TAGE) in z15. 17

- In z14, both a neural-network-based perceptron engine for enhanced direction prediction and a simple call-return stack for target prediction are introduced for additional accuracy

- Only branch targets of > 512 byte-blocks away will be considered as a potential call-return pair

- The branch prediction logic communicates its prediction results to the instruction fetching logic through an overflow queue (BPOQ); such that the branch prediction pipeline will not be directly coupled to and be potentially throttled by instruction fetch operations (e.g., during an I-cache miss).

# **Figure 3: Branch Prediction Structure**

#### **Table 1: Branch Prediction Resources**

| Label        | Structure Name                                                  | Description                                                                                                             | z196                           | zEC12    | z13                        | z14                        | z15                           |

|--------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------|----------------------------|----------------------------|-------------------------------|

|              |                                                                 |                                                                                                                         | Rows x Sets (where applicable) |          |                            |                            |                               |

| ВТВР         | Branch Target Pre-<br>buffer                                    | 0.5th level branch instruction address and target predictor. Look-up in parallel to BTB1, upon usage, transfer to BTB1  | NA                             | 128 x 6  | 128 x 6                    | 128 x 6                    | NA                            |

| BTB1         | L1 Branch Target Buffer                                         | 1st level branch instruction address and target predictor                                                               | 2048<br>x 4                    | 1024 x 4 | 1024 x 6                   | 2048 x 4                   | 2048 x 8                      |

| BHT1         | L1 Branch History<br>Table                                      | 1st level direction predictor (2-bit): weakly, strongly taken, or not-taken                                             | 2048<br>x 4                    | 1024 x 4 | 1024 x 6                   | 2048 x 4                   | 2048 x 8                      |

| BTB2         | L2 Branch Target Buffer                                         | 2 <sup>nd</sup> level branch instruction address and target history buffer                                              | NA                             | 4096 x 6 | 16K x 6                    | 32K x 4                    | 32K x 4                       |

| BHT2         | L2 Branch History<br>Buffer                                     | 2 <sup>nd</sup> level direction 1-bit predictor for branches not predicted ahead of time                                | 32 K                           | 32 K     | NA                         | NA                         | NA                            |

| ACC          | Column Predictor<br>(z13+) / Fast Re-<br>indexing Table (zEC12) | Accelerate BTB1 throughput in finding the<br>"next" branch                                                              | NA                             | 64       | 1024<br>(search-<br>based) | 1024<br>(stream-<br>based) | 1024 x 8                      |

| SBHT/<br>PHT | Speculative BHT & PHT                                           | Speculative direction prediction with transient updates at (out-of-order) resolution time prior to actual completion    | 3+2                            | 3+2      | 8+8                        | 8+8                        | 8+8                           |

| PHT          | Pattern History Table                                           | Pattern-based tagged direction prediction                                                                               | 4096                           | 4096     | 1024 x 6                   | 2048 x 4                   | 512 x 8 x 2<br>(short & long) |

| СТВ          | Changing Target Buffer                                          | Pattern-based target prediction predicts branches with multiple targets, typically subroutine returns and branch tables | 2048                           | 2048     | 2048                       | 2048                       | 2048                          |

| SMRU         | Super MRU table (z13+)                                          | Protect certain branches from normal LRU out to make the BTBP more effective                                            | NA                             | NA       | 128                        | 128                        | NA (no<br>BTBP)               |

#### **Instruction Delivery**

- Since z/Architecture instructions are of variable lengths (2, 4 or 6 bytes), an instruction can start at any halfword (integral 2-byte) granularity

- Instruction fetching logic fetches "chunks" of storage-aligned instruction data from the instruction cache, starting at a disruption point, e.g., after a taken branch (including subroutine calls and returns) or after a pipeline flush

- Up to 2 16-byte chunks for z196 and zEC12 and up to 4 8-byte chunks for z13 and after

- These "chunks" of instruction data are then written into an instruction buffer (as a "clump") where instructions are extracted (or parsed) into individual z-instructions in program order

- The instruction decode logic then figures out high-level characteristics of the instructions and which/how the execution engines will handle them

- Is it a storage access? A fixed-point instruction? Which execution units will be involved?

- Is it a branch-type instruction? If yes, did the branch prediction logic predict that? If not, notify the branch prediction logic (to restart its search) and then proceed based on predefined static prediction rules (e.g., branch-on-conditions are default to be not-taken, while branch-on-counts are defaulted to be taken)

- Is it going to be implemented in millicode? If yes, did the branch prediction logic predict that? If not, reset the front-end to start at the corresponding millicode routine entry instruction

- For a complex instruction, does it need to be "cracked" or "expanded" into simpler internal instructions, called micro-operations (μops)? For example, a LOAD MULTIPLE instruction will be expanded into multiple "load" μops that fetch from storage and write individual general registers (GRs)

- Instructions (and µops) are then bundled to form an instruction group (for pipeline management efficiency), and dispatched (written) into the instruction issue queue

#### Instruction Cracking or Expansion

- There are multiple reasons for instruction cracking or expansion

- Always (due to inherent multiple operations needed), e.g.

```

- BRANCH ON COUNT (BCTR) ------> add register with immediate value of -1

- | |-----> scratch condition code

- | | |-----> branch evaluation <-------

```

• Length based (multiple operations based on length), e.g.

- Although the processor pipeline may be "RISC-like", typical **register-storage** instructions, e.g., "ADD" in example below, are handled efficiently in the design with a feature called "dual issue", and should be used whenever appropriate

- ADD: Register1 <= Register1 + memory((Base register) + (Index register) + Displacement)</li>

Register-storage ADD (A) -----> load from storage into targe

```

- Register-storage ADD (A) ------> load from storage into target register

- | .. Some cache access cycles later

- |-----> add R1 with target register

```

The instruction is **not** considered to be cracked because it is tracked as 1 instruction by using 1 issue queue entry (and 1 global completion table entry), though it is issued to both the LSU and a non-LSU execution unit - hence it's 'dual issued'

#### **Instruction Grouping**

- Instructions (and μops) are dispatched (or written) in-order into the out-of-order issue queue as a group. They are then

tracked in the global completion table (GCT) until every instruction in the group finishes its processing. When all

instructions in a group finish processing, the group is completed and retired

- As instructions (and μops) are grouped, they are subject to various grouping rules, which prevent certain instructions (and μops) from being grouped with others

- During a dispatch cycle, z196 and zEC12 support one group of up to 3 instructions, while z13..z15 allow two groups of up to 3 instructions

- Some basic rules of grouping

- Simple instructions, including most "register-register" and "register-storage" type instructions, can be grouped

- Branch instructions, if second in the group, or if predicted taken, will be the last instruction in the group

- · Best group size if taken branches are the third in a group

- μops that are expanded from the same instruction will usually be grouped

- But not with other instructions (or μops) in z196, zEC12

- If expanded into only 2 μops, can be grouped with one other simple instruction after (in z13, z14)

- Storage-storage instructions are usually grouped alone, except for the µops that they may be expanded into

- Other instructions that are alone in a group:

- Register-pair writers, e.g., DIVIDE (D, DR, DL, DLR), MULTIPLY (M, MR)

- Non-branch condition code readers, e.g., ADD LOGICAL WITH CARRY (ALC\*), SUBTRACT LOGICAL WITH BORROW (SLB\*)

- · Explicit floating-point control register readers or writers

- · Instructions with multiple storage operands

- EXECUTE or EXECUTE RELATIVE instruction or its target

- Since z13, max group size will be 2 if any μop has more than 3 register sources (including Access Register usage in AR mode)

#### **Instruction Dispatching**

- As instructions are dispatched, the source and target architected registers are renamed into a virtual pool of physical registers and are tracked accordingly

- The amount of rename tracking resources (how many in-flight mappings can be tracked) and physical registers available are key factors of the effectiveness of an out-of-order design

- In z196 and zEC12, the mapping tracker (the mapper) consists of 1 bucket of 48 mappings

- GRs: 1 mapping per each 32-bit register write, 1 mapping per each full 64-bit register write

- FPRs: 1 mapping per each 32-bit register write, 1 mapping per each full 64-bit register write

- ARs: 1 mapping per each 32-bit register write

- Since z13, the mapping tracker consists of 2 buckets of 64 mappings each = 128 total mappings

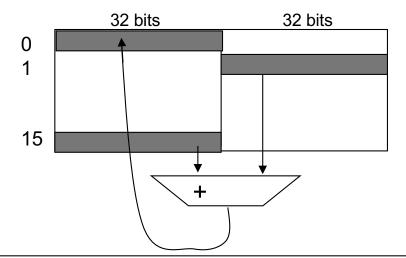

- GRs: 1 mapping per each 32-bit register write, the GR #'s LSB decides which bucket to use; a 64-bit register write will require 2 mappings, one from each bucket

- FPRs: 1 mapping per each write, the FPR #'s 2<sup>nd</sup> LSB decides which bucket to use

- ARs: 1 mapping per each write, the AR #'s LSB decides which bucket to use

- Since z13, multiple writes to the same register in the same group does not require separate trackers

- Instructions in a group are dispatched into one of the two issue queues (side 0 and side 1).

- The total size of issue gueue directly relates to the overall out-of-order window and thus affects performance

- In z196 and EC12, only one instruction group can be written into one of the two queue sides in any cycle; in an alternating fashion

- Since z13, two groups can be written in any cycle with one group into each side; with the older group on side 0

- The issue queue includes a dedicated "virtual branch queue" since zEC12, 1 per side, that handles relative branch instructions whose targets are less than 64 Kilobytes away

- These branches will alternate to the different sides of the virtual branch queue independently of the other instructions in the group

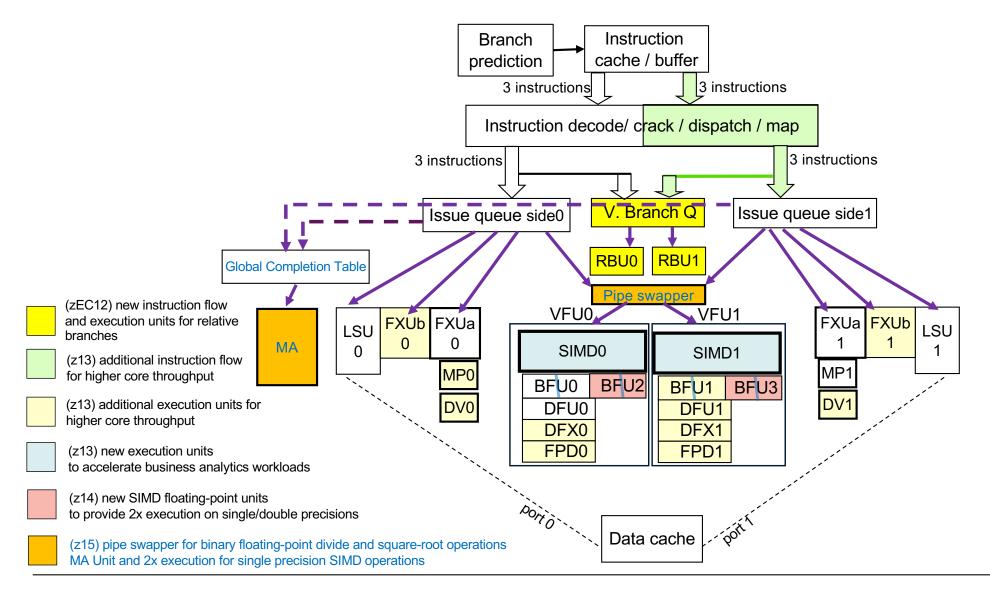

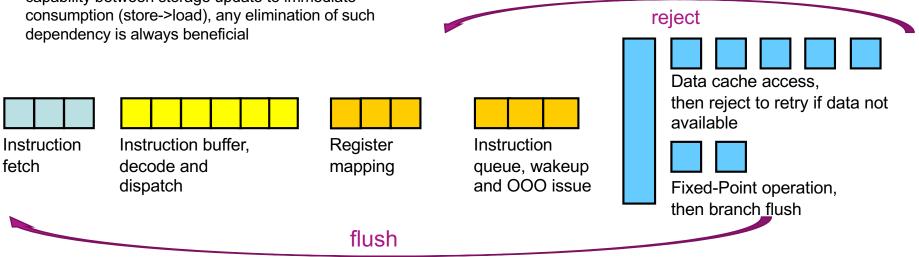

#### Instruction Issue and Execution

- After instructions are dispatched into the issue queues, the issue queues will issue the oldest (and ready) instruction from each issue port to the corresponding execution engine

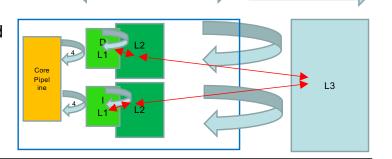

- Each issue-queue side is connected to a number of specific processing engines, using z15 as an example in Fig. 4,

- There are 5 issue ports (per side; 10 total per core); each to a different engine, including

- A relative branch unit (RBU) handles relative branches

- A GR writing fixed-point unit (FXUa) handles most of the fixed-point arithmetic and logical operations, and also includes a

multiply engine (MP) and a divide engine (DV) (both being non-blocking)

- A non-GR writing fixed-point unit (FXUb) handles other fixed-point operations that do not write any GR results

- A load/store unit (LSU) port, with accesses to the operand data-cache, handles memory accesses

- A vector & floating-point unit (VFU) handles complicated operations

- Inside each of the **VFU**, there are multiple engines that execute different functions in parallel to each other

- **BFU** that handles both hexadecimal and binary (IEEE standard) floating-point arithmetic operations, and vector floating-point operations

- **DFU** that handles decimal (IEEE standard) and quad-precision floating-point arithmetic operations; and since z14, BCD vector convert, multiply, and divide operations

- SIMD that further consists of multiple subunits: PM engine that performs vector permute functions; XS engine that

performs fixed-point arithmetic and logical functions; XM engine that performs several multiply functions and ST engine

that performs string-related functions

- **DFX** that handles decimal (BCD) fixed-point arithmetic operations, and since z14, simple BCD vector operations

- FPD that handles divide and square root operations for both binary and hexadecimal floating-point arithmetic

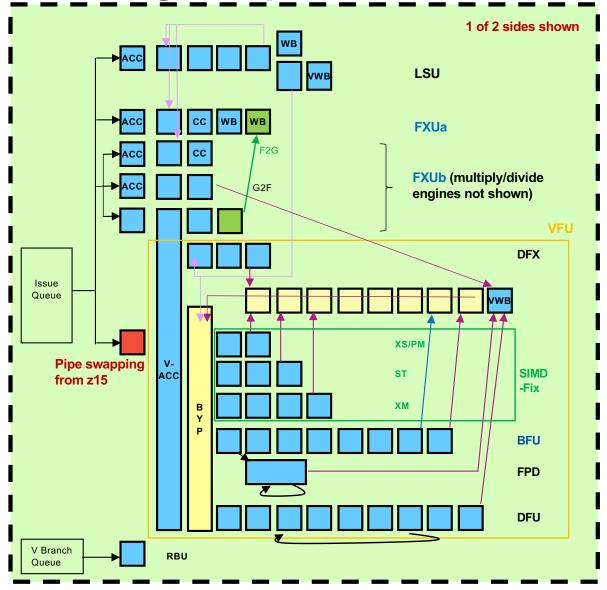

- Typical pipeline delays through each of the execution engines are shown in Fig. 5

- Differences vs. z14, z13, zEC12, and z196 are shown as colored boxes in Fig. 4

- Starting with z15, a modulo arithmetic (MA) unit can execute micro-operations sent from the global completion table (instead of the issue queues) to accelerate elliptic curve cryptography (ECC) as directed by millicode.

## Figure 4: z15 high-level instruction & execution flow

# Figure 5: z14/z15 Execution Engine Pipelines

#### Only 1 of 2 issue sides shown

- Typical pipeline depths and bypass capabilities shown

- Some instructions may take longer to execute or bypass results

- · Access registers not shown

ACC – GR access WB – GR write back

V-ACC – FPR/VR access VWB – FPR/VR write back

CC - condition code calculation

BYP - data bypass network cycle

FPD, DFU – functions, e.g., divide, square-root, may take multiple passes through the pipeline

G2F – GR to VR/FPR moves F2G – VR/FPR to GR moves

#### **Table 2: Out of order resources**

|                                | z196                                                               | zEC12                                                                         | z13                                                                                                   | z14                                               | z15                                                                      |

|--------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------|

| GR                             | 80 (16<br>permanently<br>reserved for<br>millicode)                | 80 (up to 16<br>reserved for<br>millicode) +<br>16 immediate<br>value entries | 120 (up to 16 reserved for each thread while in millicode) + 8 immediate value entries                | Same as z13                                       | Same as z13                                                              |

| FPR /<br>VR(z13)               | 48 FPRs                                                            | 64 FPRs                                                                       | 127 FPRs / VRs (up<br>to 8 reserved for<br>each thread while in<br>millicode)<br>+ a zero-value entry | Same as z13                                       | Same as z13                                                              |

| AR<br>(access<br>register)     | 56 (16<br>permanently<br>reserved for<br>millicode)                | 56 (16<br>permanently<br>reserved for<br>millicode)                           | 96 (up to 8 reserved for each thread while in millicode)                                              | Same as z13                                       | Same as z13                                                              |

| Issue<br>Queue                 | 20 x 2 sides                                                       | 20 x 2 sides +<br>12 x 2 sides of<br>Branch Queue                             | 30 x 2 sides +<br>14 x 2 sides of<br>Branch queue                                                     | 30 x 2 sides +<br>16 x 2 sides of<br>Branch queue | 36 x 2 sides +<br>16 x 2 sides of<br>Branch queue                        |

| Global<br>Completion<br>Table  | 24 x 3<br>instructions<br>(complete up to 3<br>instructions/cycle) | 30 x 3 instructions (complete up to 3 instructions/cycle)                     | 24 x 2 x 3<br>instructions<br>(complete up to 6<br>instructions / cycle)                              | Same as z13                                       | 30 x 2 x 3<br>instructions<br>(complete up to 6<br>instructions / cycle) |

| Unified<br>Mapping<br>Trackers | 48                                                                 | 48                                                                            | 64 + 64                                                                                               | Same as z13                                       | 4 x 60 (new design)                                                      |

#### The load/store unit

- The load/store unit (LSU) handles the operand data accesses with its L1 data-cache and the tightly coupled L2 data-cache

- The L1 data cache has 2 access ports, and each port can support an operand access of data elements of up to 8 bytes a cycle

- There is no performance penalty on alignment except for when the element crosses a cache line boundary

- Prior to z15, vector elements of more than 8 bytes are accessed in two successive cycles

- Starting with z15, vector loads using doubleword or quadword alignment hints can be accessed in one cycle

- In addition to the prefetching of cache misses as part of the natural behavior of the out-of-order pipeline

- LSU supports software prefetching through PREFETCH DATA type instructions

- LSU also includes a stride-prefetching engine that prefetches +1, +2 cache-line strides, when a consistent stride is detected between cache miss address patterns at the **same** instruction address across loop iterations

- To minimize pipeline bubbles typically caused by "store-load" dependencies through storage, LSU provides a sophisticated bypass network to bypass pending storage updates that are not yet available in the L1 cache into dependent loads as if the operand data was in L1 (subject to certain limitations). But in general,

- Data should be bypass-able even if bytes are required from different storing instructions for a load request

- Data should be bypass-able if the store data is ready a small number of cycles before the dependent load request

- Multiple mechanisms are used to predict dependencies (based on prior pipeline processing history) between load and store instructions, and will stall load instructions just long enough to enable "perfectly" timed bypasses

- If a store operation is performed after its dependent load (due to out-of-order operations), a flush occurs

- If a store operation is performed before its dependent load and the data is not bypass-able (due to timing or hardware limitations), the load is rejected and retried

#### **On-chip Core Co-Processor**

- On-chip core co-processors (COPs) are available to enable hardware acceleration of data compression, cryptography, and, on zEC12 and after, Unicode conversions

- Each COP is private to each core since zEC12, but is shared by two cores in z10 and z196

- The co-processor also handles COMPRESSION CALL (CMPSC) instruction that compresses data and cryptographic functions (under the CPACF facility, next page) that support latest NIST standards

- In addition, Unicode UTF8<>UTF16 conversions are supported in zEC12; and since z13, all Unicode conversions (UTF 8<>16<>32) are supported

- Starting with z15, the co-processor provides support for SORT LISTS (SORTL) instruction that can turn up to 128 lists of

unsorted input data into one or more lists of sorted output data. It also provides a means to merge multiple lists of sortedinput data into a single list of sorted-output data.

- Co-processors are driven through commands of millicode, as it emulates the corresponding complex z instruction

- Millicode interprets the instruction, tests storage areas, and sets up the co-processor

- Millicode fetches the source operand

- Millicode writes source operand data into the co-processor to be processed

- Millicode sets up result storage areas for co-processor to use often it is the actual target areas

- Coprocessor works on the instruction with the provided source data and generates output data

- For CMPSC, the coprocessor will also fetch dictionary tables accordingly

- Co-processor writes into the pre-set result storage areas

- In some cases, millicode will transfer the Co-processor results to the target areas

- Millicode analyzes status information from the co-processor and repeats work if needed

- Millicode ends when the instruction (or a unit-of-operation) is completed

- In SMT mode (since z13), the co-processor handles one thread at a time. If the second thread requires the COP, it waits

until the first thread finishes an appropriate unit-of-operation or the whole instruction

# **CPACF - CP Assist for Cryptographic Functions**

- Also known as the Message-Security Assist (MSA) instructions

- Runs synchronously as part of the program on the processor

- Provides a set of symmetric cryptographic and hash functions for:

- Data privacy and confidentiality

- Data integrity

- Random Number generation

- Message Authentication

- Enhances the encryption/decryption performance of clear-key operations for

- SSL/TLS transactions

- Virtual Private Network (VPN)-encrypted data transfers

- Data storing applications

- Since z15, (not shown in table to the right), an extension 9 is provided to support for elliptic curve cryptographic authentication of messages, the generation of elliptic curve keys, and scalar multiplication.

- new instruction COMPUTE DIGITAL SIGNATURE

AUTHENTICATION (KDSA) supports the ECDSA and EdDSA

algorithms using curves P-256, P-384,P-521, Ed25519, and Ed448

- compliant with the Digital Signature Standard (DSS), National Institute of Standards and Technology (NIST) July 2013

- Existing PERFORM CRYPTOGRAPHIC COMPUTATION instructions (PCC and PCKMO) are also modified

|   | Supported      | Clear | Protected | \ |

|---|----------------|-------|-----------|---|

|   | Algorithms     | Key   | Key       |   |

| ı | DES, T-DES     | Υ     | Υ         |   |

|   | AES128         | Υ     | Υ         |   |

|   | AES192         | Y     | Υ         |   |

|   | AES256         | Υ     | Υ         |   |

|   | AES-GCM(z14)   | Υ     | Υ         |   |

|   |                | V     | NI/A      |   |

|   | GHASH          | Y     | N/A       |   |

|   | SHA-1          | Y     | N/A       |   |

|   | SHA-256        | Y     | N/A       |   |

|   | SHA-384        | Υ     | N/A       |   |

|   | SHA-512        | Υ     | N/A       |   |

|   | SHA-3 224 (z14 | .) Y  | N/A       |   |

|   | SHA-3 256 (z14 | .) Y  | N/A       |   |

|   | SHA-3 384 (z14 | .) Y  | N/A       |   |

|   | SHA-3 512 (z14 | ,     | N/A       |   |

|   | PRNG           | Υ     | N/A       |   |

|   | DRNG           | Y     | N/A       |   |

|   | TRNG (z14)     | Y     | N/A       |   |

| 1 |                |       |           |   |

#### **On-chip Integrated Deflate Accelerator**

- On z15, with the Integrated Accelerator for zEnterprise Data Compression, the industry standard compression offered through the zEnterprise Data Compression (zEDC) Express PCIe I/O card is now built into the z15 chips

- Data compressed with the zEDC Express adapter can be read and decompressed with the new Integrated Accelerator for zEDC on z15 and vice versa

- A single compression acceleration engine, called the Nest Accelerator Unit (NXU), is provided on each CP chip

- The NXU is directly connected to the shared on-chip L3 cache and operate in tandem w/ the processor core (thread) that is currently running the new DEFLATE CONVERSION CALL (DFLTCC) instruction

- DFLTCC is interpreted by the millicode and executed in NXU

- Millicode manages the locking mechanism which enables a single core to use NXU at a given time

- Millicode divides bigger data into 256KB chunks for timesharing and combines the result

- Millicode tests source data area, history area, target data area and creates a data structure with all the control information

- Millicode enqueues the source and target address to the accelerator and sends a start operation signal

- NXU fetches the control block, history data, source data and compress/decompress the data and writes the result to target data area

- NXU also provides the status and writes back the resulted control block

- Millicode analyses the status and control block and repeats/continue/finishes the instruction, report the result to software

#### **Instructions of Interest**

- We will discuss some of the instructions in z/Architecture and their handling that might be of general interest:

- Simple instructions, including descriptions of some interesting ones

- Special Storage-to-Storage instructions

- MOVE LONG instructions

- High Word instructions

- Conditional instructions

- EXECUTE instructions

- BRANCH PREDICTION PRELOAD instructions

- DATA PREFETCH instructions

- NEXT INSTRUCTION ACCESS INTENT instruction

- Atomic and locking instructions

- And a few architecture features:

- Hardware Transactional Execution

- Guarded Storage Handling

- Secure Execution

- Vector (SIMD) instructions

- BCD Vector Instructions

- And some storage usage model highlights

#### **Simple Instructions**

#### Simple instructions

- Fixed-point results are bypassed without delay into the next dependent fixed-point instruction if the instructions are in the same side of the issue queue; otherwise, there will be at least a one-cycle delay

- An instruction with a storage access operand will need to wait for 4 cycles if the operand is a hit in L1 data cache

- An operand written by a store instruction to a storage address followed by a load instruction of the same address will require at least 2 to 4 cycles to be bypassed as L1 cache hit data

- Floating-point instructions are generally pipelined but can be of different latencies. The design forwards dependent data as soon as it is available

- Non-floating-point vector (SIMD) instructions (since z13) have shorter latencies than floating-point ones

- SIMD results are also bypassed when available

- Destructive and non-destructive instructions

- Many z/Architecture instructions specify just two operands, with one operand doubling as both a source and a target

- These instructions are shorter (in length) and occupy less space in storage

- If a register-based operand that will be overwritten is still required after an instruction execution, software must first make a copy of the register before the overwriting instruction

- Many non-destructive instructions were introduced since z196, such that the register copy operations can be avoided

- Load and Store Reversed instructions

- To facilitate conversion between big-endian (BE) and little-endian (LE) formats, a few instructions (LOAD REVERSED and STORE REVERSED) are provided to reverse the byte ordering of a data element to/from memory

- Both load and store operations are supported

- 2, 4, and 8-byte operands are supported

- MOVE INVERSE is also available for more than 8-bytes storage to storage data swap

- Millicode implements this instruction by doing a byte-by-byte copy

- Starting with z15, vector enhancements facility 2 includes new instructions (VECTOR LOAD/STORE BYTE/ELEMENTS

REVERSED ELEMENT<S> <AND ZERO/REPLICATE>) to load or store elements or arrays of elements in the little-endian

format through the vector registers

#### **Special Storage-to-Storage Instructions**

- z/Architecture includes a set of storage-storage instructions in which the data size is specified in the instruction as the length field

- Mostly defined to be left-to-right and byte-at-a-time operations

- Special hardware is being used to speed up certain common cases

- MOVE Characters (MVC)

- If <= 16 bytes, it is cracked into separate load and store µops</li>

- If > 16 bytes, it is handled by sequencing logic inside the LSU

- If the destination address is 1 byte higher than the source address (and they overlap), it is special cased into hardware as a 1-byte storage-padding function (with faster handling)

- If the destination address is 8 bytes higher than the source address (and they overlap), it is special cased into hardware as an 8-byte storage-padding function (with faster handling)

- For other kinds of address overlap, it will be forced into millicode to be handled a byte at a time

- Since z10, special case detection is done at decode time, not detected during address generation, and thus requires the instructions to have B1=B2

- COMPARE LOGICAL Characters (CLC)

- If <= 8 bytes, it is cracked into separate load and compare μops</li>

- If > 8 bytes, it is handled by the sequencing logic inside the LSU

- EXCLUSIVE OR Characters (XC)

- If <= 8 bytes, it is cracked into separate load and "or-and-store" μops</li>

- If > 8 bytes and if base register values and displacement values are equal, i.e., an exact overlap on addresses, it is special

cased into hardware as a storage clearing function (with faster handling)

- Since z10, this special case detection is done at decode time, not detected during address generation, and thus requires the instructions to have B1=B2 and D1=D2

- If > 8 bytes and no exact overlap on addresses is detected, it is handled by sequencing logic inside the LSU

- For other kinds of address overlap, it will be forced into millicode to be handled a byte at a time

- AND Characters (NC) and OR Characters (OC) instructions are implemented similarly, without the special clearing function

## **MOVE LONG Instructions (MVCL\*)**

- MOVE LONG instructions can copy a large amount of data from one storage location to another

- A special architected functional variant can also be used to pad storage

- · These instructions are implemented in millicode

- A special engine is built per CP chip for aligned copying or padding functions at a page granularity

- The page-aligned copying or padding is done "near memory", instead of through caches, if

- Not executed inside a transaction

- Padding character specified is neither X'B1' nor X'B8'

- A preceding NIAI instruction does not indicate that the storage data will be used subsequently

- · The operands must not have an access exception

- Length >= 4K bytes

- For moves, source and destination addresses are both 4K-byte aligned

- · For padding, destination address is 4K-byte aligned

- Otherwise, the move process will operate through the caches (L1, L2...)

- Note that the evaluation is revised every unit-of-op

- For padding, even if starting address is not aligned, millicode pads in cache to the first 4K-byte boundary, then uses "near memory" pad engine for the next aligned 4K-byte pages until the remaining length is less than 4K bytes. After that, padding is done in cache again

- Near-Memory engine usage is best when the amount of data involved is large and the target memory is not to be immediately consumed in subsequent processes

- Since the special engine is shared within a CP chip, contention among processors is possible

- Such contention is handled transparently by millicode, and additional delay may be observed

<sup>\*</sup> Further discussion about MVCL vs. MVCLE in "Frequently Asked Questions (7)"

# **High Word Instructions**

- Provided since z196

- Intended to provide register-constraint relief for compilers

- High words of GRs are made independently accessible from the low words of GRs

- Software can use up to 32 word-based GRs, 16 doubleword-based GRs, or combination of word and doubleword GRs

- For register dependencies, including address-generation interlocks, the high-word GRs are treated separately from the low-word GRs

- Various types of operations are supported

- Add, subtract, compare, rotate, load, store, branch-on-count

#### **Conditional Instructions**

- In many applications (for instance, sorting algorithms), conditional-branch outcomes are highly data dependent and thus highly unpredictable

- A mispredicted branch can result in a pipeline flush, and may incur many cycles of branch correction penalty

- A limited set of conditional load/store instructions are provided (z196+) where the execution is predicated on the condition code

- Highly unpredictable branches can be replaced with conditional instructions

- In the example, the old code shows a COMPARE register instruction (CR) followed by a BRANCH ON CONDITION instruction (BRNE for BC), and a LOAD instruction (L) that may or may not be executed depending on the outcome of the branch

- The new code sequence replaces the branch and load instructions with a LOAD ON CONDITION (LOC) instruction

- It is cracked into a load from storage and a conditional select μop

- The conditional select μop uses the condition code to select between the original register value and the new value from storage

- This sequence now avoids potential branch wrong flushes

NOTE: Access exceptions may be reported whether the storage content is effectively accessed or not

```

Old Code

R1, R3

BRNE skip

R4, (address X)

skip

R4, R3

New Code

R1, R3

LOC R4, (address X), b'_{1000}

R4, R3

*Pseudo-code for illustration only

```

#### **EXECUTE Instructions**

- "Execute" instruction is commonly used\* with targets being storage-related instructions (e.g., MVC, CLC mentioned before) where the length field (specifying the number of bytes) can be substituted with the contents of a general register (GR) without actually modifying the instruction in memory (and without explicit branch to or from the 'target' instruction)

- "Execute" is handled by the processor like a branch, by

- Jumping to the target of the execute instruction as a branch target, and fetching it

- Decoding and executing the target instruction (modifying as needed)

- Immediately returning back to the subsequent instruction after the "execute" (except when the target is a taken branch itself)

- This "implied" branch handling is supported by the branch prediction logic to reduce the overall processing delay

- Certain pipeline delay is required between the reading of the GR and the "modification" of the target instruction

- The delay is reduced since z13 for a selected group of instructions: MVC, CLC, and TRANSLATE AND TEST (TRT)

- When the operand length is mostly random during run-time, the alternative of using a branch table is not preferred due to its potential inaccuracy in branch prediction

```

Example where MVC's length depends on compare of R1 and R3:

LHI R4, x'1'

LHI R5, x'2'

CR R1, R3

LOCR R4, R5, b'1000'

EX R4, move

...

move MVC 0(length, R13), 0(R14)

*Pseudo-code for illustration only

```

\*other **tricky** EXECUTE usages are not discussed here; e.g., in modifying register ranges, lengths of operand 1 or operand 2, and branch masks

#### **BRANCH PREDICTION PRELOAD Instructions**

- BRANCH PREDICTION PRELOAD (BPP) and BRANCH PREDICTION RELATIVE PRELOAD (BPRP) instructions

introduced with zEC12 specify the location of a future to-be-taken branch and the target address of that branch

- By providing such directives to the hardware's branch prediction logic, the limitation of the hardware branch table's capacity may be overcome

- The processor may now predict the presence of branches without having seen them before or if their history was displaced

- The directives will not override or modify an existing hardware history entry's target address

- As described earlier, the branch prediction logic should always search ahead 'asynchronously' of where in the program instructions are currently being decoded and executed

- Just like requesting a stop on a bus, the request needs to be activated BEFORE the bus passes the desired stop; to be effective,

the preload instruction needs to be executed **before** the prediction logic may search pass the branch address to be effective

- The preload instructions are thus best used when the program's run-time behavior involves a lot of somewhat cold modules;

such that (taken) branches are likely not being predicted and the instructions are likely not in the cache; such that the preload instructions can have a good chance of being executed AHEAD of the search logic

- The actual usage of the preload instruction is therefore most effective when in conjunction with profile-directed feedback (PDF),

or in a JIT environment where the run-time characteristic can be extracted and analyzed

- The more (taken) branches in-between and the further away in sequential memory address, the more likely a preload will succeed

- At a minimum, the target branch should be more than 1 (taken) branches and 256 sequential bytes away

- The relative form of preload instruction, BPRP, should be used if possible as it can be activated earlier in the pipeline, providing a better chance of being effective

- The preload mechanism may also perform an instruction cache touch (and thus a potential prefetch) on the branch target

- Do not use for purely instruction cache prefetches, as that will pollute the branch prediction history structure

#### **PREFETCH DATA Instructions**

- Starting with z10, PREFETCH DATA (PFD) and PREFETCH DATA RELATIVE LONG (PFDRL) instructions were

introduced to enable program code a way to manipulate the local data cache

- · It is architecturally a no-op

- The provided prefetch function allows code to potentially acquire a cache line (into L1) in a correct cache state (for readonly or for write) ahead of the actual load/store instructions that will access the data

- Note: prefetching a cache line that is contested among multiple processors is usually a bad idea

- These prefetch instructions not only allow operand data prefetching, but they also provide a way to release a local cache line's ownership (also known as untouch)

- The untouch function is to allow software code to proactively release (or invalidate) its ownership (from the processor that it is running on) of a specified cache line; as such it can be used when <u>done using</u> a shared data structure

- Such that, when a different processor accesses this same cache line some time later, the shared cache (L3/L4) will not need to spend time in removing the line from this "last-owning" processor before granting ownership to the "newly-requesting" processor

- These directives should be used carefully, and some experimentation may be required to yield desired performance effect

- Prefetch function can be redundant with given hardware capabilities

- The out-of-order pipeline inherently performs "baseline" prefetching

- · The stride-prefetch engine also prefetches cache lines based on fetching patterns and miss history

- The L4 cache does limited prefetching from memory based on certain miss criteria

- Prefetch can hurt if the cache line is contested with other processors

- Untouch function can be tricky to use

- If it is a highly contested cache line, demote operation might hurt (by adding more related operations to the system)

- If the cache line is cold, it might not matter

- In general, the demote variant (code 6) is preferred to the full untouch variant (code 7) since it usually incurs less overhead; as it can be used when done updating a shared data structure

- NOTE: EXTRACT CPU ATTRIBUTE (ECAG) instruction should be used, instead of hardcoding any cache-related attributes, to minimize the chance of observing adverse effects on different hardware models

## **NEXT INSTRUCTION ACCESS INTENT (NIAI) Instruction**

- The NIAI instruction was introduced in zEC12 for program code to provide some hints to the cache system on the intention of the next immediate instruction's operand accesses, so the hardware can adjust its related handling

- The instruction behaves like a "prefix" instruction but architecturally it is a separate (no-op) instruction

- · Hints will also be passed into instructions that are implemented in millicode

- The cache subsystem provides heuristic to maintain cache ownership among multiple processors

- Upon a cache miss from a "current" processor core for a "fetch-only" (non-storing) instruction, the cache subsystem may return

an exclusive state if the cache line was previously updated by a "previous" processor

- This design anticipates that this "current" processor will likely follow suit of the "previous" processor and store to the cache line

after this fetch-only miss, saving coherency delays (otherwise seen when changing from a shared state to an exclusive state)

- In the case where the heuristic is not working perfectly, e.g., when there are multiple "readers" on a cache line, the NIAI instruction (code 1 "write") can be used by a "writer" process to indicate subsequent store intention upon an initial fetch

- The NIAI instruction can also be used to indicate "truly read-only" usage of a cache line.

- Given the "reader and writer" processes described above, a NIAI (code 2 "read") can be used to specify the read-only intention of the consumer (or reader) process's accesses to a cache line; thus, preventing the line from potentially migrated to the reading processor as exclusive (write) ownership

- The hint can now help reduce the coherency penalty on the next round when the producer (or writer) process is writing into the cache line again

- Cache lines are usually managed from most recently used (MRU) to least recently used (LRU) in the cache, so lines that

have not been used recently are evicted first when new cache lines are installed

- This scheme generally works well, but is suboptimal in cases where the process is operating on streaming data where data is only accessed once and then becomes uninteresting

- In these streaming cases, it is desirable to label such data as LRU so that it's not retained at the expense of other data that will be used again

- The NIAI instruction (code 3 "use once") can be used to indicate streaming data accesses such that the local cache will keep those data in compartments that will be evicted sooner

#### **Atomic and Locking Instructions**

- z/Architecture provides a set of instructions that can be used for atomic operations

- e.g., TEST AND SET (TS), COMPARE AND SWAP (CS)

- They check a value in storage (fetch) and then conditionally update the storage value (store) such that the fetch and the store

are observed to be "atomic", meaning to an outside observer the two actions appear to have occurred simultaneously

- The Interlocked-Access Facility instructions were added on z196

- Load and "arithmetic" instructions for unconditional updates of storage values

- · (Old) storage location value loaded into GR

- Arithmetic or logical operation (add, and, xor and or) result overwrites value at storage location

- · Best for unconditionally updating global information, like a counter or a flag

- Interlocked storage updates with an immediate operand are also supported

- Supported operations include add, and, xor and or

- LOAD PAIR DISJOINT (LPD, LPDG)

- · Load from two different storage locations into GR N, N+1

- · Condition code indicates whether the fetches were atomic

- Hint: For software locks, if the lock is likely concurrently used by multiple processors (i.e., often contested), the following sequence should be considered

- It is more desirable to test the lock value before using atomic instruction (e.g., CS) to set the lock

```

LHI R2, 1

: value to set lock

R1, lock

; load from memory and test value; always test first

LOOP

LT

; serialization to quarantee getting new value

BCR 14,0

; repeat if non-zero

JN7

LOOP

R1, R2, lock; set lock if lock was empty

JNE LOOP

; retry if lock became set

*Pseudo-code for illustration only

*See additional discussion in "Frequently Asked Questions (2)"

```

### **Hardware Transactional Memory**

- Beginning in zEC12, z/Architecture supports hardware transactional (memory) execution through the <u>transaction</u> e<u>xecution</u> facility, occasionally referred to as TX

- A group of instructions can be observed to be performed with atomicity, or not done at all (aborted)

- Non-transactional stores are allowed within a transaction

- A form of constrained transaction (transaction with restrictions) is also supported where the hardware will automatically retry an aborted/failed transaction until the transaction is successful

- Optional detail debug data can be provided

- Transaction usage is not advisable if the contention of used storage is already high

- Likely end up wasting CPU cycles if the transaction keeps aborting due to real-time cross-CPUs memory access contentions

- Aborts are expensive (>200 cycles) and worse if abort debug information is requested

- Hint: compute complex results outside of a transaction, then use transaction with only a small number of instructions to check data, and then store the results away

- Access (fetch) footprint\* is limited by L2 cache associativity and size

- Up to 1 Mbyte in zEC12, 2 Mbyte in z13, 4 Mbyte in z14..z15

- Update (store) footprint\* is limited by L2 cache associativity and size of an internal store buffer

- The buffer design can support up to 64 blocks of 128-byte (storage-aligned) data changed within a transaction

- The L1 data cache is updated as each store instruction completes within a transaction, but L2 cache update from the buffer is deferred until transaction completes

- Note: Access footprint may be counted for fetches done through mispredicted branches. Footprint limitations are shared by the 2 threads when SMT2 is enabled such that effective footprint may be smaller than when one thread is running

### **Guarded Storage Handling**

- Beginning in z14, z/Architecture provides the guarded-storage facility for programming languages to more efficiently implement storage-reclamation techniques commonly referred to as garbage collection (GC)

- Allows application/user threads to continue running concurrently during phase of GC compaction

- Accomplished by providing hardware-assisted read barriers for guarded storage (GS) involved in a compaction event

- Prior to compaction, software defines a "range of guarded-storage segments" by specifying the GS starting/ending

address and segment size to cover the entire region containing all guarded segments. A bit mask vector is set to define

which segments are protected.

- Done through the LGSC (LOAD GUARDED STORAGE CONTROLS) and STGSC (STORE GUARDED STORAGE CONTROLS) instructions

- When guarded storage is set up and enabled

- When the second operand of the LGG (LOAD GUARDED) or LLGFSG (LOAD LOGICAL AND SHIFT GUARDED) instruction designates a GS segment as specified by software, a guarded-storage event is recognized, and control is passed to a guardedstorage event handler

- Otherwise, the respective instructions perform their defined load operations

- All other instructions that access a segment of guarded storage are unaffected by the facility

- Only the new LGG and LLGFSG instructions can potentially generate a guarded-storage event

- It is expected that the problem-state guarded-storage event handler would

- First save program GRs, move offending data to a non-guarded area and fix up any pointer addresses if necessary

- Then after restoring program GRs, it will branch back to the interrupted program address previously saved during the GS event and continue normal program operations

- NOTE: Some refer to this feature as 'pause-less garbage collection', where 'pause-less' should be understood to mean 'less-pausing' and \*not\* 'pause-free'

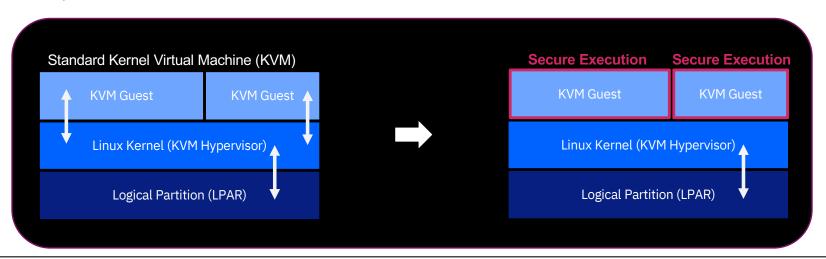

#### **Secure Execution**

- Beginning with z15, a hardware-based security technology, called Secure Execution (SE) architecture, is introduced

- Secure Execution

- Provides a virtual machine that is fully isolated and protected from the hypervisor with encryption keys that only the IBM z

hardware and firmware have access to

- Enables hosted workloads to process unencrypted memory securely without exposing it to the host or any other workloads in the same environment

- As an example, KVM guests enabled in secure execution mode will have their memory and execution states protected

- Secure memory can only be accessed in secure mode

- Instructions are only executed from the secure memory of the guest in secure mode

- A new trusted firmware layer called the Ultravisor sits between the hardware and hypervisor to implement high-level security requirements, e.g., encrypting memory blocks before export (paging), and decrypting them on import

- Although there will be some modest overhead passing controls through the Ultravisor, application performance should perform similarly while in SE mode vs. not in SE mode

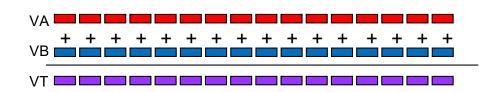

## Single-Instruction-Multiple-Data (SIMD)

- SIMD instructions, sometimes also referred to as vector instructions, were introduced in z13

- See Eric Schwarz's Journal article<sup>11</sup> for deeper overview

More instructions are added with z14 and z15, but only a selected set will be discussed here\*\*

- To support these instructions, new vector registers (VRs) are architected

- 32 x 128-bit architected registers are defined per thread

- FPRs overlay VRs as follows:

- FPRs 0-15 == Bits 0:63 of SIMD registers 0-15

- Update to FPR <x> alters entire SIMD register <x>